The CPU and surrounding components

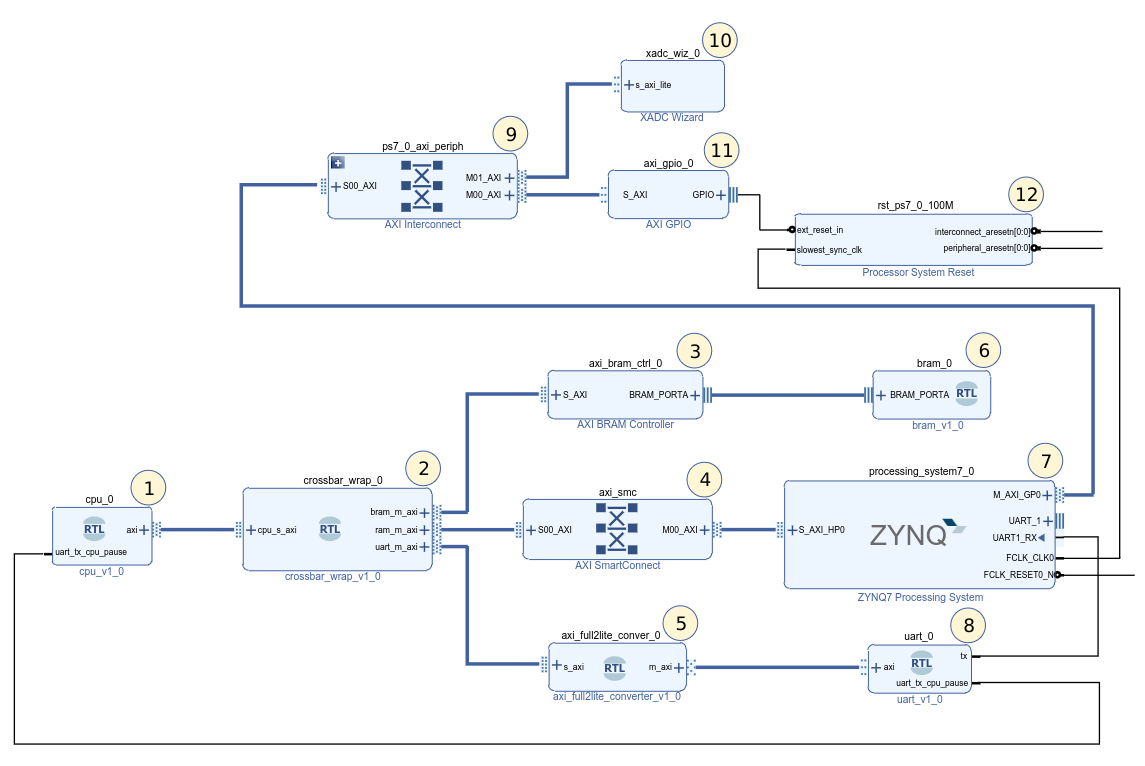

The platform whose block design is illustrated below, is a minimal System-on-a-Chip (SoC) design written in VHDL which consists of the following components:

- a 32-bit MIPS processor core - cpu (component 1),

- a boot memory - bram (component 6) and its controller (component 3),

- a unified 2-KB cache - included in cpu,

- a DDR memory and its controller -included in the Zynq PS (component 7), and

- a Universal Asyncronous Receiver/Trasmitter (UART) unit - uart (component 8).

Component 10 consists of sensors and an analog to digital converter that are used for the energy

evaluation.

Components 2, 4, 5, 9 are either interconnects or interface protocol converters.

The Zynq PS - component 7 - generates the clock signal for all the platform components,

and the reset signal for the components 9 to 11.

Then component 12 generates the reset signal for the rest of the platform.

The cpu - component 1 - is based on the open-source Plasma cpu and interfaces available on the OpenCores and GitHub websites.

The original Plasma design was updated for our purpose and tailored for the Pynq-Z1 board.

All components marked with RTL are VHDL modules with source code given,

while all the other components are Intellectual Property (IP) cores provided by Xilinx.

Using the mlite CPU emulator

An emulator of the mlite CPU is provided to debug the benchmarks or derive runtime statistics such as instruction usage. To run the emulator for a specific benchmark, one change needs to be made in the common Makefile. In '/benchmarks/Makefile.commmon', change line 88 from '../../tools/mlite.exe (IMG_FILE) B'. Now, in the directory of a specific benchmark such as '/benchmarks/pi, run the following:

make clean image

make test_sim

If you want to change the behaviour of the emulator, you can do so by altering and re-compiling 'emulator/mlite.c'.