Synthesizing your Design

To synthesize and implement your design, open the Vivado project file (zynq_fpga.xpr) in the folder

fpga/zynq_fpga.

The Flow Navigator pane (left of the window) contains all the available FPGA implementation flow steps.

Using this pane works in a number of steps:

- functional verification

- updating the block diagram to reflect the parameters settings from the simulation block diagram and validating this

- generating the bitstream

This is accomplished from the Flow Navigator pane, either step by step allowing to analyze the results of each step:

SYNTHESIS → Run Synthesis;IMPLEMENTATION → Run Implementation;PROGRAM AND DEBUG → Generate Bitstream

Or directly by clicking PROGRAM AND DEBUG → Generate Bitstream,

which will automatically execute all the previously mentioned steps.

Upon a successful completion the bistream file (.bit) will be created.

Normally, block diagram output products necessary for synthesis are automatically re-generated every time. However, if for some reason the older files are used, the output products can be forcefully re-generated prior to running synthesis by selecting in the Flow Navigator pane

IP INTEGRATOR → Generate Block Designand then selecting Global as the Synthesis Options.

Vivado FPGA Implementation Strategies

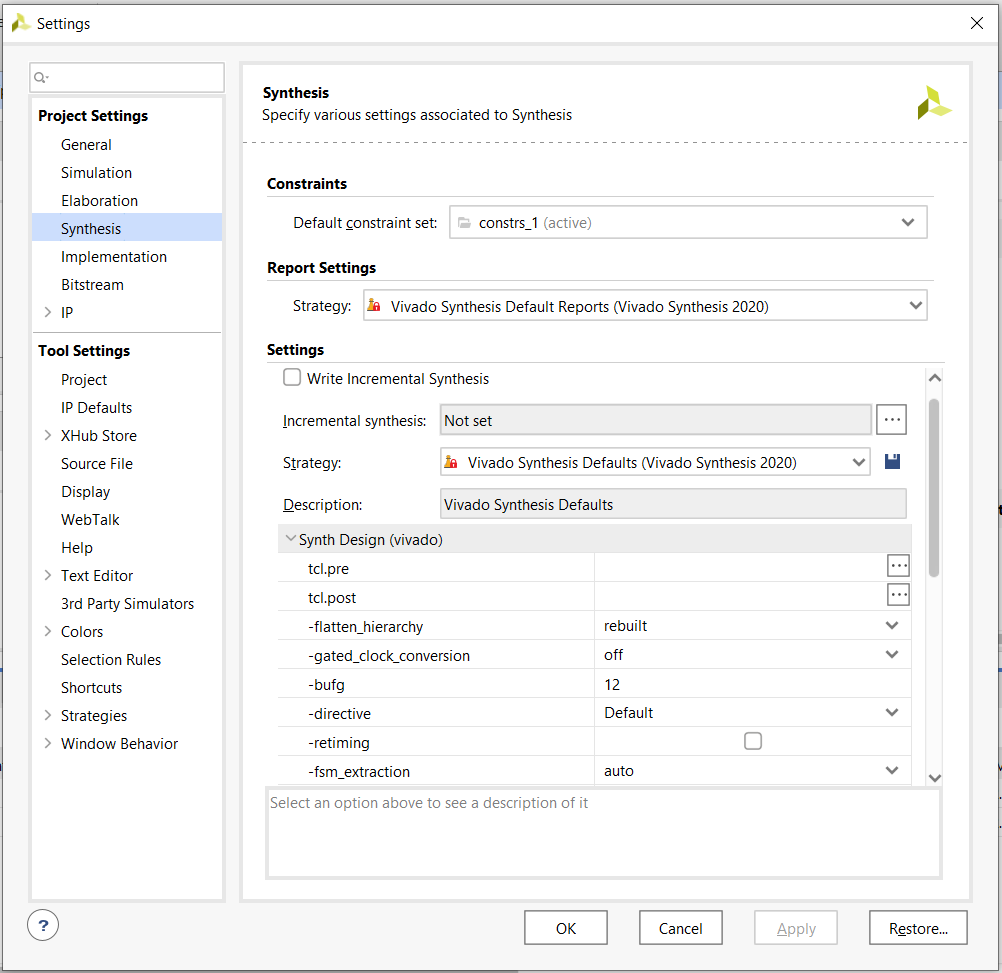

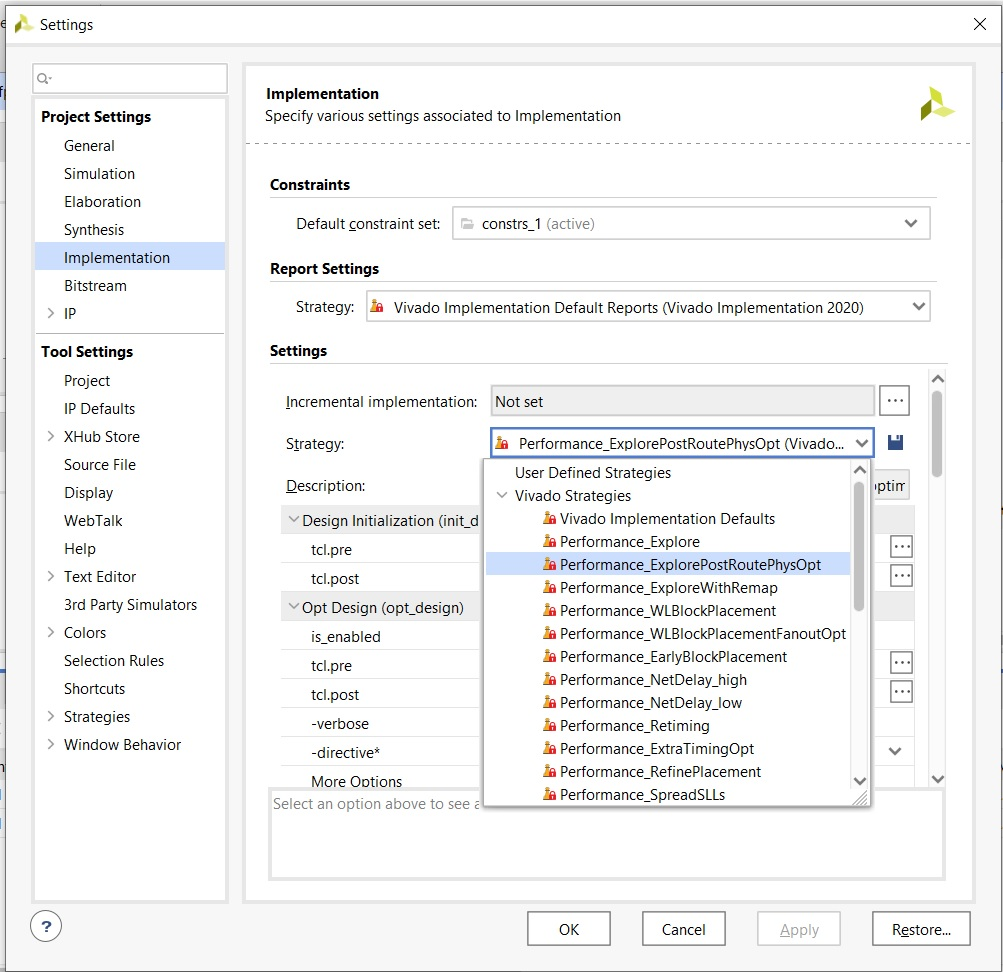

Depending on the algorithms and overall strategies selected within the Vivado tool synthesis and implementation* menu, slightly different FPGA implementations (with different area utilization and timing performance) can be obtained.

A strategy is a set of Vivado tool settings,

which specify the design flows and the optimization levels.

Vivado provides a set of predefined strategies for synthesis and implementation.

Alternatively, you can also create your own strategies

Vivado's Synthesis & Implementation settings, displayed below,

can be accessed from the Flow Navigator pane via Settings.

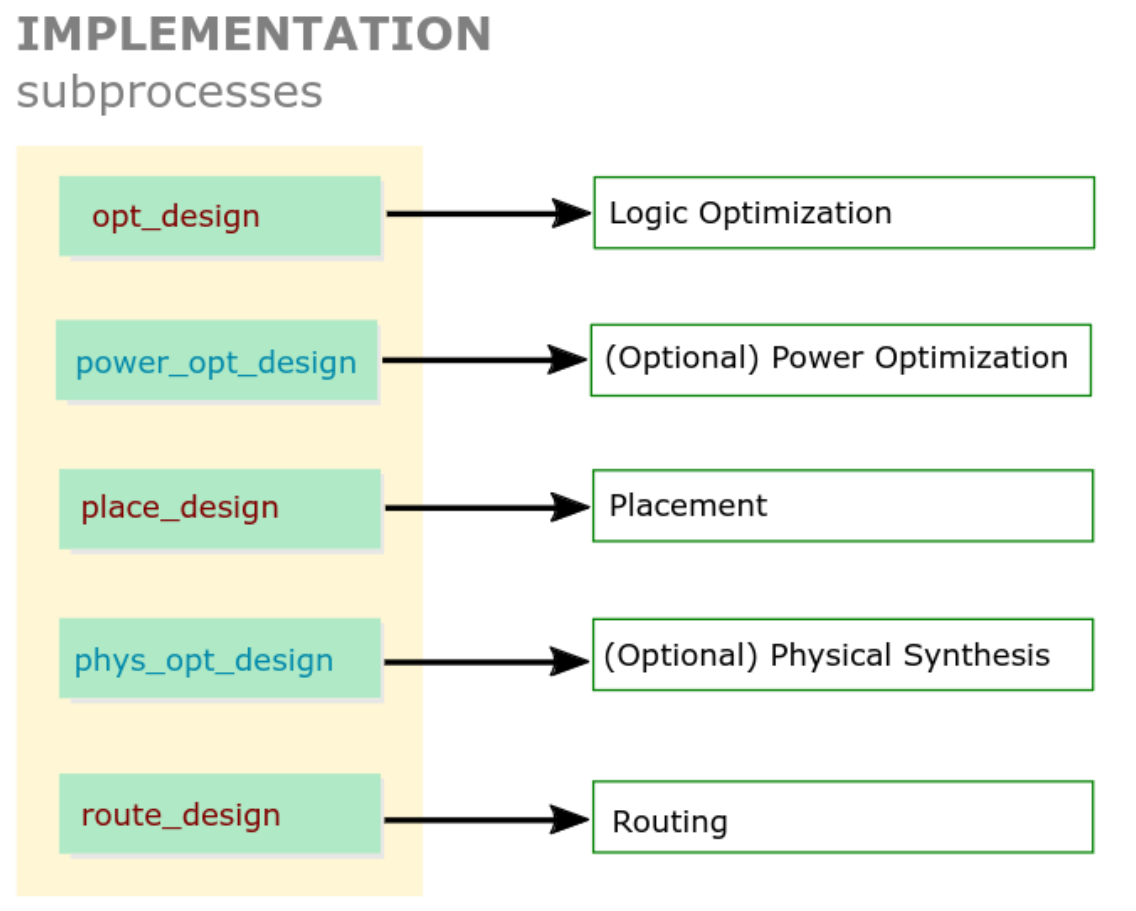

While synthesis consists of just a single subprocess,

the implementation step has multiple such subprocesses,

each consisting of a series of steps which can be optimized with specified effort level (-directive setting).

Identifying effective strategies can lead to best results based on specified design goals.

For example, you can use this when you have a performance oriented goal.

By changing the Synthesis and Implementation strategy,

minor timing closure violations (e.g., small negative slack) can be resolved.

This can even lead to a higher maximum clock frequency for the design.

For further details about the Vivado tool Synthesis and Implementation strategies, please refer to the

Vivado Design Suite User Guide - Synthesis and

Vivado Design Suite User Guide - Implementation.